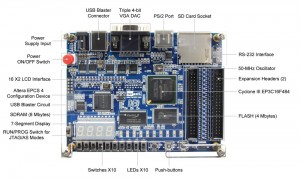

I also have a Terasic DE0 FPGA board.

Since I had started with a Xilinx board, and I really wanted to get to know both Xilinx and Altera, I bought this Altera board.

You can see the important specs on the board, but some things I like:

72 usable I/O pins

4-bit VGA instead of 1-bit on the Xilinx board. This gives 2^(4*3) colors or 4096 colors! Yay! Much better than 8!

It’s got an SD card slot.

PS2, VGA, plenty of switches…

It’s got a reasonable size FPGA on it. This is my most recent board and most of my new designs have been using this board.

Altera’s software is much less of a brute than Xilinx’s ISE, and it compiles faster. It sucks because the web version(free) limits you to one core and I’m on quad-core machine.

But I’ve been very happy with the board. I’ve managed to get a working SDRAM controller on it too!

My amiga video scan converter project is based on this board.

I bought the Terasic DE0 a little while back.

This board is pretty decent, and I’ve used it for a few different projects.

Regarding documentation, the docs are overall pretty good. Pretty much everything you need is either available at Terasic site if it’s a board-specific item, or at Altera’s if it’s FPGA specific.

I don’t think I’ve looked for one thing ever that simply was missing, or wrong. There was one thing I suggested they add as an FAQ, and despite the fact that they told me they would, they haven’t.

If you need to use pin K22, you need to look here

https://quartushelp.altera.com/current/mergedProjects/comp/comp/comp_tab_dp_dual-purpose.htm

and set the nCEO (or was it NCSO) pin as regular I/O.

Otherwise: you’ll get a multiple drivers error during compilation, even though YOU aren’t driving it more than once.

This is important for VGA applications and affects one of the BLUE signals.

The user manual pretty much gives you everything you need

The control panel is useful, but I think a lot of the sample apps use NIOS, and unless you are going that route, the example code isn’t helpful.

Quartus II (free version) is pretty decent, at least in comparison to Xilinx’s ISE (that I haven’t used in a couple versions). It’s smaller, faster, lighter, and so on.

These tools are PIGS in general, so it’s all relative.

Learn how to use SignalTap II, the built in the logic analyzer, and life is very good.

Memory controllers are the bain of FPGA hobbyists, I made minor changes to one I found online, and it works fine on the DE0. I’d give the link, but it seems to have gone offline. I’m working on a local mirror on my site.

(https://web.archive.org/web/20130123011711/https://whoyouvotefor.info/altera_sdram.html)

Yes, SRAM is easier, but usually less plentiful. There aren’t many other options if you want a decent amount of memory.

Here’s 16-channels of 5v conversion for $15 off the shelf

https://www.seeedstudio.com/depot/logic-sniffer-16bit-input-buffer-wing-p-721.html?cPath=61_68

Here’s what I created

https://techtravels.org/?p=488

Works pretty decent

Recommend

https://www.amazon.com/Bebop-Boolean-Boogie-Third-Edition/dp/1856175073/ref=sr_1_1?ie=UTF8&qid=1367202219&sr=8-1&keywords=bebop+to+the+boolean+boogie

and

https://www.amazon.com/FPGA-Prototyping-Verilog-Examples-Spartan-3/dp/0470185325/ref=sr_1_3?s=books&ie=UTF8&qid=1367202247&sr=1-3&keywords=fpga+by+example

or similar.

As posted on Classic Computer Mailing List